双边沿乒乓架构提升毫米波时钟性能

聚焦5.5G/6G无线通信及下一代高速串行接口,针对毫米波本振时钟超低抖动的严苛需求,中国科学院微电子研究所与清华大学合作,在亚采样锁相环(SSPLL)技术上取得重要突破。

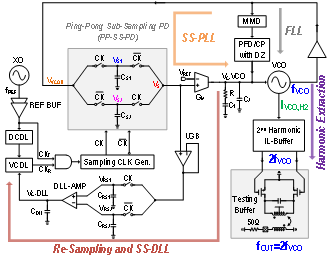

乒乓亚采样锁相环电路结构

传统SSPLL虽具高鉴相增益优势,但在环路带宽、带内相位噪声与参考杂散之间存在难以兼顾的设计折衷。为此,团队创新提出“双边沿乒乓亚采样锁相环”架构,通过同时利用参考时钟的上升沿和下降沿,实现等效参考频率倍频,有效缓解上述矛盾,显著提升环路性能。

此外,团队还开发了一种高功率与面积效率的注入锁定缓冲器,可在高效提取压控振荡器二次谐波的同时进行谐波整形,进一步抑制带外相位噪声。基于这两项核心技术,研究团队采用65nm CMOS工艺研制出一款K波段锁相环时钟芯片,输出频率覆盖22.4–25.6 GHz,整体功耗低于18 mW,RMS积分抖动优于50 fs,抖动—功耗优值(FoM)达到−254 dB以下。

该成果为未来6G通信、太赫兹系统及超高速数据接口提供了高性能、低功耗的时钟解决方案。